## Halting Problem Proof from Finite Strings to Final States

When we understand that every potential halt decider essentially derives a formal mathematical proof from its inputs to its final states previously undiscovered semantic details emerge. When-so-ever the potential halt decider cannot derive a formal proof from its input strings to its final states of Halts or Loops, undecidability has been decided.

The formal proof involves tracing the sequence of state transitions of the input TMD as syntactic logical consequence inference steps in the formal language of Turing Machine Descriptions.

The proof would essentially be a hypothetical execution trace\*\* of the state transition sequences of the input TMD. It cannot be an actual execution trace or the halt decider could have non-halting behavior. \*\*Like step-by-step mode in a debugger.

If the first element of the input finite string pair is a correct TMD then this proof must necessarily proceed from the specified TMD start state through all of the state transitions of this TMD to the halting or looping behavior of this TMD.

The following has been adapted from material from the this book: An Introduction to Formal Languages and Automata by Peter Linz 1990 pages 318-320

We begin our analysis by constructing a hypothetical halt decider: H.

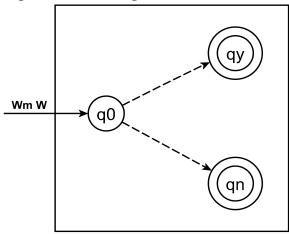

## Figure 12.1 Turing Machine H

The dashed lines proceeding from state (q0) are represented in the text definition as the asterisk  $\vdash^*$  wildcard character. These conventions are used to encode unspecified state transition sequences.

#### **Definition of Turing Machine H (state transition sequence)**

H.q0 Wm W  $\vdash^*$  H.qy // Wm is a TMD that would halt on its input W H.q0 Wm W  $\vdash^*$  H.qn // else

The diagram and the state transition sequence indicate that H begins at its own start state H.q0 and is applied to finite string pair (Wm, W).

Then it proceeds through an unspecified set of state transitions to one of its final states.

H.qy is the final state of H indicating that Wm is a TMD would halt on input W. H.qn is the final state of H indicating that Wm is Not a TMD that would halt on input W.

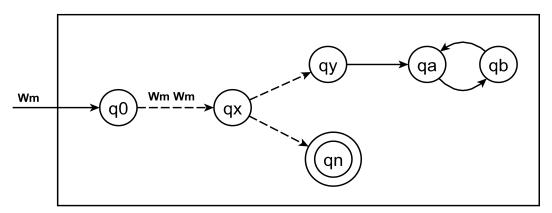

In an attempt to provide a valid counter-example proving by contradiction that a Halt Decider cannot possibly exist for every possible TM / Input pair we create Turing Machine  $\hat{H}$  by making the following changes to H:

(1) Ĥ copies its input Wm a its Ĥ.q0 state and transitions to its Ĥ.qx state.

(2)  $\hat{H}$  would begin to evaluate Wm Wm at its  $\hat{H}$ .qx state in exactly the same way that H would begin to evaluate its Wm W input at its H.q0 state.

(3) States (qa) and (qb) are appended to existing final state ((qy)) such that any transition to state (qy) will cause  $\hat{H}$  to loop.

Since Turing Machine  $\hat{H}$  is created by adapting H, it would have exactly the same behavior at its  $\hat{H}$ .qx state as H would have at its H.q0 state.

Figure 12.3 Turing Machine Ĥ

## Definition of Turing Machine Ĥ (state transition sequence)

Ĥ.q0 Wm ⊢\* Ĥ.qx Wm Wm ⊢\* Ĥ.qy ∞ Ĥ.q0 Wm ⊢\* Ĥ.qx Wm Wm ⊢\* Ĥ.qn

If Turing Machine H is applied to Turing Machine descriptions  $[\hat{H}]$   $[\hat{H}]$  would H transition to H.y or H.n ?

H [Ĥ] [Ĥ2] // We append a "2" to the second Ĥ for clarity

Because H is performing a mathematical proof on finite strings  $[\hat{H}]$   $[\hat{H}2]$  the required syntactic logical inference chain is simply the state transitions that  $[\hat{H}]$  would make on its input  $[\hat{H}2]$ . In simplest terms H is performing a step-by-step debug trace of  $[\hat{H}]$ .

## Step-by-step debug trace of what [H] would do on its input [Ĥ][Ĥ2]

(01) H begins at its start state H.q0.

(02) H begins to evaluate what [Ĥ] would do on its input [Ĥ2].

# Step-by-step debug trace of what [Ĥ] would do on its input [Ĥ2]

- (03) [Ĥ] would begin at its start state [Ĥ].q0

- (04) [Ĥ] would make a copy of its input [Ĥ2], we will call this [Ĥ3].

- (05)  $[\hat{H}]$  would transition to its state  $[\hat{H}]$ .qx.

- (06) [Ĥ] would begin to evaluate what [Ĥ2] would do on its input [Ĥ3].

# Step-by-step debug trace of what [Ĥ2] would do on its input [Ĥ3]

(07) [Ĥ2] would begin at its start state [Ĥ2].q0

- (08) [Ĥ2] would make a copy of its input [Ĥ3], we will call this [Ĥ4].

- (09) [Ĥ2] would transition to its state [Ĥ2].qx.

- (10) [Ĥ2] would begin to evaluate what [Ĥ3] would do on its input [Ĥ4].

## Can you see the infinite recursion?

H [ $\hat{H}$ ] [ $\hat{H}$ ] specifies an infinitely recursive evaluation sequence. Every HP proof by contradiction depends this same infinite recursion. What no one ever noticed before is that the debug trace by the halt decider must abort its evaluation long before it ever reaches the appended infinite loop. Because the formal proof is aborted before ever reaching the final states of H, H is not a decider for H [ $\hat{H}$ ] [ $\hat{H}$ ].

Because of this every TMD in the infinitely recursive sequence is defined in terms of H each would reject the whole sequence as semantically incorrect before even beginning any halting evaluation, and transition to H.qn.

As further evidence that infinitely recursive evaluation sequence has been overlooked we only need to know that every TMD always requires its own TM / Input pair. For any finite sequence of input H could always decide halting.

If  $\hat{H}$  did not copy its input and instead simply took two inputs then the Halting Decision would be easy.  $\hat{H}$  would transition to its  $\hat{H}$ .qy state because  $\hat{H}$ 2 would transition to its  $\hat{H}$ 2.qn state on null input. This would cause H to transition to its H.qn state deciding halting for [ $\hat{H}$ ] [ $\hat{H}$ 2].

## **Turing Machine Description Language**

(Generalized from: TM, The Turing Machine Interpreter by David S. Woodruff)

The following is space delimited 'quintuples', each one of which is a five-symbol Turing Machine instruction. It is written in AWK regular expression syntax.

1) Initial State

2) Current Tape Symbol

3) Next State

4) Write Tape Symbol

5) Move Tape Head Left or Right

--1-- --2-- --3-- --4-- --5--[0-9]+ [\x20-\x7e] [0-9]+ [\x20-\x7e] [LR]

If we make a fixed number of (hexadecimal) states then The UTM could simply hold a sorted list of std::strings. A sorted list would allow state transitions to occur by binary search. This would allow a very simple DFA based syntax checker.

The tape could be constructed using a std::vector. Binary Zero end markers would be in the tape alphabet and not the input alphabet. These trigger memory reallocation to enlarge the tape.

## Postscript November 2018 (Halting Problem Solution)

#### Definition 9.1 (Linz 1990 page 233)

A Turing Machine M is defined by:  $M = (Q, \Sigma, \Gamma, \delta, q0, [], F)$  where Q is a finite set of internal states,  $\Sigma$  is a finite set of symbols called the input alphabet,  $\Gamma$  is a finite set of symbols called the tape alphabet,  $\delta$  is the transition function,  $[] \in \Gamma$  is a special symbol called blank,  $Q0 \in Q$  is the initial state,  $F \subseteq Q$  is the set of final states.

The Halting Problem is defined as follows:

Given the description of a Turing machine M and an input w, does M, when started in initial configuration q0w perform a computation that eventually halts? (Linz 1990 page 317)

Provability() is defined in the language of Turing\_Machine\_Descriptions: ⊢™D

$\forall M \in TMD \ \forall w \in Finite\_Strings(\Sigma)$ Halts(M, w)  $\leftrightarrow (\vdash TMD unify\_with\_occurs\_check(M, w) \land \vdash TMD halts(M, w))$

The higher order logic predicate: Halts(M, w) is materially equivalent to the existence of a formal proof in the language of Turing Machine Descriptions:

// Test input pair (M, w) for valid input (see details below)

from the q0w start state to the unify\_with\_occurs\_check(M, w) state

// Then decide halting for input pair: (M, w) then from the unify\_with\_occurs\_check(M, w) state to the final halts(M, w) state

Implementing the functional equivalent of the Prolog predicate unify\_with\_occurs\_check/2 in a halt decider enables every self-referential halting problem proof counter-example Turing machine description to be rejected as structurally unsound.

When fully appreciating this insight we realize that Rice's Theorem would be refuted if the nontrivial property of halting decidability could always be correctly decided.

#### Clocksin and Mellish 2003, Programming in Prolog Using the ISO Standard Fifth Edition Chapter 10 The Relation of Prolog to Logic, page 254.

According to the formal definition of Unification, this kind of "infinite term" should never come to exist. Thus Prolog systems that allow a term to match an uninstantiated subterm of itself do not act correctly as Resolution theorem provers.

the built-in predicate unify\_with\_occurs\_check/2 ... fails if an occurs check detects an illegal attempt to instantiate a variable.

Since an "infinite term" does not specify a Turing machine description that would halt on its input the following Turing machine specification would be a halt decider:

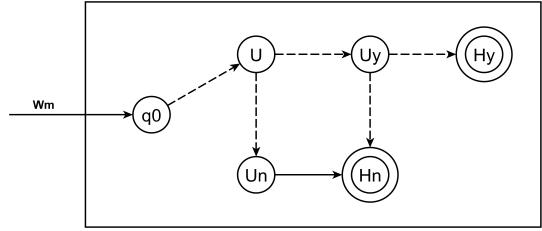

# **Definition of Turing Machine HD (state transition sequence)**

HD.q0 Wm W  $\vdash$ \* HD.Unify\_with\_occurs\_check.yes  $\vdash$ \* HD.halts.yes HD.q0 Wm W  $\vdash$ \* HD.Unify\_with\_occurs\_check.yes  $\vdash$ \* HD.halts.no HD.q0 Wm W  $\vdash$ \* HD.Unify\_with\_occurs\_check.no  $\vdash$  HD.halts.no

## Figure 12.4 Turing Machine HD

Copyright 2004, 2006, (2012 through 2018) Pete Olcott