## Halting problem undecidability and infinitely nested simulation

The standard pseudo-code halting problem template "proved" that the halting problem could never be solved on the basis that neither value of true (halting) nor false (not halting) could be correctly returned to the confounding input.

This problem is overcome on the basis that the halt decider aborts its simulation of this input before ever returning any value to this input. It aborts the simulation of its input on the basis that its input specifies what is essentially infinite recursion to any simulating halt decider.

```

procedure compute_g(i):

if f(i, i) == 0 then

return 0

else

loop forever  // (Wikipedia:Halting Problem)

```

When halting is defined as any computation that halts without ever having its simulation aborted then it can be understood that partial halt decider H correctly decides that its input does not halt on the simplified version of the Linz Ĥ.

The x86utm operating system was created so that the halting problem could be examined concretely in the high level language of C. UTM tape elements are 32-bit unsigned integers. H examines the behavior of the x86 emulation of its input. As soon as a non-halting behavior pattern is matched H aborts the simulation of its input and decides that its input does not halt.

A simulating halt decider H is a Universal Turing Machine (UTM) that has been adapted to decide whether or not its input halts. H simulates the execution of its inputs exactly as if it was simply a UTM. After H simulates each instruction of its input it examines the full execution trace of this input. When an execution trace matches an infinite execution behavior pattern H aborts the simulation of this input and reports that this input does not halt.

This halt deciding principle overcomes the conventional halting problem proofs: It is self-evidently true that every computation that never halts unless its simulation is aborted <is> a non-halting computation even after its simulation has been aborted.

```

// Simplified Linz A (Linz:1990:319)

void P(u32 x)

{

u32 Input_Halts = H(x, x);

if (Input_Halts)

HERE: goto HERE;

}

int main()

{

H((u32)P, (u32)P);

}

```

# So can you describe the exact conditions which cause H to detect a repeated state and declare that the program will never terminate?

Anyone knowing the x86 language well enough can examine the two x86 execution traces of **H(P,P)** and directly see for themselves that it is completely certain that the input to **H(P,P)** would never halt unless the simulation of this input its was aborted.

It analyzes the currently updated stored execution trace of the simulation of its input after it simulates each instruction of this input. Because H only needs to get very few inputs correctly it only needs to correctly recognize very few infinitely repeating patterns: Simple infinite recursion and simple infinite loops.

For H to recognize the infinitely repeating pattern of P it only needs to see that same thing that humans see when they examine the x86 execution trace of the simulation of P.

P continues to call H with its own machine address endlessly repeating its first 8 lines of x86 code. There is no code that can escape this endlessly repeating cycle in these 8 lines of x86 code.

```

_P()

[00000af8](01)

[00000af9](02)

[00000afb](01)

[00000afc](03)

[00000b00](03)

[00000b03](01)

[00000b09](03)

[00000b06](03)

[00000b13](02)

[00000b17](02)

[00000b13](01)

[00000b13](01)

Size in bytes:

_P()

push ebp

mov ebp,esp

8bec

push ecx

51

mov eax,[ebp+08]

push eax

8b4508

50

8b4d08

mov ecx, [ebp+08]

51

push ecx

e81ffeffff call 00000928 // Machine address of H

83c408

add esp,+08

8945fc

mov [ebp-04],eax

cmp dword [ebp-04],+00 jz 00000b17

837dfc00

7402

ebfe

imp 00000b15

8be5

mov esp,ebp

pop ebp

5d

с3

ret

Size in bytes:(0035) [00000b1a]

_main()

[00000b28](01)

[00000b29](02)

[00000b2b](05)

[00000b30](05)

[00000b35](05)

[00000b3d](02)

[00000b3f](01)

[00000b40](01)

push ebp

8bec

mov ebp,esp

68f80a0000 push 00000af8 // Machine address of P 68f80a0000 push 00000af8 // Machine address of P e8eefdffff call 00000928 // Machine address of H

83c408

add esp,+08

33c0

xor eax.eax

5d

pop ebp

Size in bytes: (0025) [00000b40]

```

#### Columns

- (1) Machine address of instruction

- (2) Machine address of top of stack

- (3) Value of top of stack after instruction executed

- (4) Machine language bytes

- (5) Assembly language text

### The above eight instructions of P are repeated here

```

[00000af8][0025bfa6][0025bfaa] 55 push ebp

[00000af9][0025bfa6][0025bfaa] 8bec mov ebp,esp

[00000afb][0025bfa2][0024bf76] 51 push ecx

[00000afc][0025bfa2][0024bf76] 8b4508 mov eax,[ebp+08]

[00000aff][0025bf9e][00000af8] 50 push eax // P

[00000b00][0025bf9e][00000af8] 8b4d08 mov ecx,[ebp+08]

[00000b03][0025bf9a][00000af8] 51 push ecx // P

[00000b04][0025bf96][00000b09] e81ffeffff call 00000928 // H

Local Halt Decider: Infinite Recursion Detected Simulation Stopped

```

In column 3 of the prior two push instructions we can see that P pushed its own machine address 0xaf8 onto the stack thus calling H(P,P) at 0x928 in an infinitely repeating cycle of the first eight x86 instructions of P.

The call to H from P only shows the first instruction of P because H ignores its own execution trace. The first thing that H does is simulate its input. So when P calls H all we see is H simulating P.

```

[00000b3a][001014de][00000000] 83c408 add esp,+08 [00000b3d][001014de][00000000] 33c0 xor eax,eax [00000b3f][001014e2][00100000] 5d pop ebp [00000b40][001014e6][00000060] c3 ret Number_of_User_Instructions(25) Number of Instructions Executed(26445)

```

When a chain of function calls specifies infinite recursion is broken by a simulating halt decider aborting the simulation of any one of these function calls, then the whole chain of function calls is correctly decided to specify a computation that does not halt.

This same reasoning applies to the computation: P((u32)P); when P() invokes H() with its own machine address, this is the first invocation of an infinite chain of invocations. As the first element of an infinite chain of invocations where the third element of this chain is aborted the whole chain is understood to specify an infinite invocation sequence.

```

void P(u32 x)

u32 Input_Halts = H(x, x);

if (Input_Halts)

HERE: goto HERE;

int main()

H((u32)P);

_P()

[00000af8](01)

[00000af9](02)

[00000afb](01)

[00000afc](03)

[00000b00](03)

[00000b03](01)

[00000b09](03)

[00000b06](03)

[00000b13](02)

[00000b17](02)

[00000b13](01)

[00000b13](01)

Size in bytes:

push ebp

8bec

mov ebp,esp

push ecx

51

mov eax, [ebp+08]

push eax

8b4508

50

mov ecx, [ebp+08]

8b4d08

51

push ecx

e81ffeffff call 00000928 // Machine address of H

83c408

add esp,+08

8945fc

mov [ebp-04],eax

837dfc00

cmp dword [ebp-04],+00

jz 00000b17

jmp 00000b15

mov esp,ebp

7402

ebfe

8be5

5d

pop ebp

c3

ret

Size in bytes: (0035) [00000b1a]

_main()

__main()

[00000b28](01)

[00000b29](02)

[00000b2b](05)

[00000b35](03)

[00000b38](02)

push ebp

55

8bec mov ebp,esp

68f80a0000 push 00000af8 // Machine address of P

e8c3ffffff call 00000af8 // Machine address of P

83c404

add esp,+04

33c0

xor eax eax

[00000b3a](01)

[00000b3b](01)

5d

pop ebp

c3

ret

Size in bytes: (0020) [00000b3b]

```

#### Columns

- (1) Machine address of instruction

- (2) Machine address of top of stack

- (3) Value of top of stack after instruction executed

- (4) Machine language bytes

- (5) Assembly language text

```

Begin Local Halt Decider Simulation at Machine Address:af8 [00000af8][0021156f][00211573] 55 push ebp [00000af9][0021156f][00211573] 8bec mov ebp,esp [00000afb][0021156b][0020153f] 51 push ecx [00000afc][0021156b][0020153f] 8b4508 mov eax,[ebp+08] [00000aff][00211567][00000af8] 50 push eax // P [00000b00][00211567][00000af8] 8b4d08 mov ecx,[ebp+08] [00000b03][00211563][00000af8] 51 push ecx // P [00000b04][0021155f][00000b09] e81ffeffff call 00000928 // H

```

## The above eight instructions of P are repeated here

```

[00000af8][0025bf97][0025bf9b] 55 push ebp

[00000af9][0025bf97][0025bf9b] 8bec mov ebp,esp

[00000afb][0025bf93][0024bf67] 51 push ecx // P

[00000afc][0025bf93][0024bf67] 8b4508 mov eax,[ebp+08]

[00000aff][0025bf8f][00000af8] 50 push eax // P

[00000b00][0025bf8f][00000af8] 8b4d08 mov ecx,[ebp+08]

[00000b03][0025bf8b][00000af8] 51 push ecx

[00000b04][0025bf87][00000b09] e81ffeffff call 00000928 // H

Local Halt Decider: Infinite Recursion Detected Simulation Stopped

```

In column 3 of the prior two push instructions we can see that P pushed its own machine address 0xaf8 onto the stack thus calling H(P,P) at 0x928 in an infinitely repeating cycle of the first eight x86 instructions of P.

The call to H from P only shows the first instruction of P because H ignores its own execution trace. The first thing that H does is simulate its input. So when P calls H all we see is H simulating P.

```

[00000b09][001014bf][00000000] 83c408

[00000b0c][001014bf][0000000] 8945fc

[00000b0f][001014bf][00000000] 837dfc

add esp,+08

mov [ebp-04].eax

837dfc00

cmp dword [ebp-04].+00

[00000b0f][001014bf][00000000]

[00000b13][001014bf][00000000]

[00000b17][001014c3][001014cf]

[00000b19][001014c7][00000b35]

[00000b1a][001014cb][00000006]

[00000b35][001014cf][00000000]

[00000b3a][001014d3][00100000]

[00000b3b][001014d3][00100000]

jz 00000b17

7402

8be5

mov esp,ebp

5d

pop ebp

ret

83c404

add esp.+04

33c0

xor eax, eax

5d

pop ebp

c3

ret

Number_of_User_Instructions(39)

Number of Instructions Executed(26459)

```

- (1) Anyone that knows the x86 language well enough can know for sure that simulating partial halt decider H must abort its simulation of P. (see the x86 execution trace of H simulating its input in H(P,P) above).

- (2) Anyone that knows the theory of computation well enough knows that any computation that never halts unless its simulation is aborted is a non-halting computation.

Putting (1) and (2) together proves that H stops its simulation of P and correctly reports that P does not halt.

# Peter Linz Ĥ applied to the Turing machine description of itself: ŵ

When we assume that the halt decider embedded in  $\hat{H}$  is simply a UTM does this define a computation that never halts when  $\hat{H}$  is applied to its own Turing machine description?

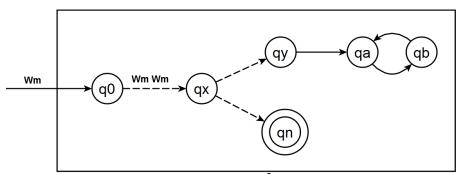

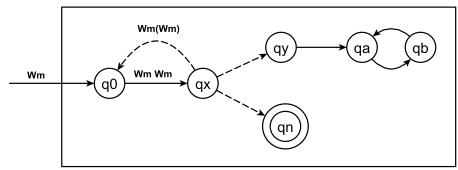

The following simplifies the syntax for the definition of the Linz Turing machine  $\hat{H}$ , it is now a single machine with a single start state. The halt decider is embedded at state  $\hat{H}$ .qx.

$\hat{H}$ .q0 wM  $\vdash$ \*  $\hat{H}$ .qx wM wM  $\vdash$ \*  $\hat{H}$ .qy  $\infty$  if M applied to wM halts, and

$\hat{H}$ .q0 wM  $\vdash$ \*  $\hat{H}$ .qx wM wM  $\vdash$ \*  $\hat{H}$ .qn if M applied to wM does not halt

Figure 12.3 Turing Machine Ĥ

Ĥ.q0 copies its input then Ĥ.qx simulates this input with the copy then Ĥ.q0 copies its input then Ĥ.qx simulates this input with the copy then Ĥ.q0 copies its input then Ĥ.qx simulates this input with the copy then... This is expressed in figure 12.4 as a cycle from qx to q0 to qx.

Figure 12.4 Turing Machine Ĥ

Within the hypothesis that the internal halt decider embedded within  $\hat{H}$  simulates its input  $\hat{H}$  applied to its own Turing machine description  $\hat{w}$  seems to derive infinitely nested simulation, unless this simulation is aborted.

**Linz, Peter 1990**. An Introduction to Formal Languages and Automata. Lexington/Toronto: D. C. Heath and Company. (318-320)

---6---

#### Theorem 12.1

There does not exist any Turing machine H that behaves as required by Definition 12.1. The halting problem is therefore undecidable.

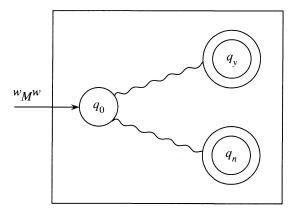

**Proof:** We assume the contrary, namely that there exists an algorithm, and consequently some Turing machine H, that solves the halting problem. The input to H will be the description (encoded in some form) of M, say  $w_M$ , as well as the input w. The requirement is then that, given any  $(w_M, w)$ , the Turing machine H will halt with either a yes or no answer. We achieve this by asking that H halt in one of two corresponding final states, say,  $q_y$  or  $q_n$ . The situation can be visualized by a block diagram like Figure 12.1. The intent of this diagram is to indicate that, if M is started in state  $q_0$  with input  $(w_M, w)$ , it will eventually halt in state  $q_y$  or  $q_n$ . As required by Definition 12.1, we want H to operate according to the following rules:

$$q_0 w_M w \not\models {}_H x_1 q_{\nu} x_2,$$

if M applied to w halts, and

$$q_0 w_M w \models {}_{H} y_1 q_n y_2,$$

if M applied to w does not halt.

Figure 12.1

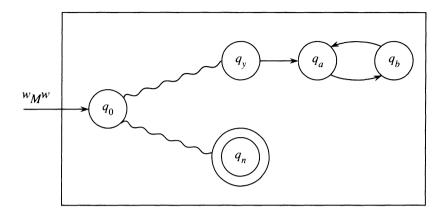

Figure 12.2

Next, we modify H to produce a Turing machine H' with the structure shown in Figure 12.2. With the added states in Figure 12.2 we want to convey that the transitions between state  $q_y$  and the new states  $q_a$  and  $q_b$  are to be made, regardless of the tape symbol, in such a way that the tape remains unchanged. The way this is done is straightforward. Comparing H and H' we see that, in situations where H reaches  $q_y$  and halts, the modified machine H' will enter an infinite loop. Formally, the action of H' is described by

$$q_0 w_M w \stackrel{*}{\models} {}_{H'} \infty$$

if M applied to w halts, and

$$q_0 w_M w \stackrel{*}{\vdash}_{H'} y_1 q_n y_2,$$

if M applied to w does not halt.

From H' we construct another Turing machine  $\hat{H}$ . This new machine takes as input  $w_M$ , copies it, and then behaves exactly like H'. Then the action of  $\hat{H}$  is such that

$$q_0 w_M \models_{\hat{H}} q_0 w_M w_M \models_{\hat{H}} \infty$$

if M applied to  $w_M$  halts, and

$$q_0w_M \stackrel{*}{\models} \hat{H}q_0w_Mw_M \stackrel{*}{\models} \hat{H}y_1q_ny_2,$$

if M applied to  $w_M$  does not halt.

Now  $\hat{H}$  is a Turing machine, so that it will have some description in  $\Sigma^*$ , say  $\hat{w}$ . This string, in addition to being the description of  $\hat{H}$  can also be used as input string. We can therefore legitimately ask what would happen if  $\hat{H}$  is applied to  $\hat{w}$ . From the above, identifying M with  $\hat{H}$ , we get

$$q_0\hat{w} \not\models \hat{H}^{\infty},$$

if  $\hat{H}$  applied to  $\hat{w}$  halts, and

$$q_0\hat{w} \models_{\hat{H}} y_1 q_n y_2,$$

if  $\hat{H}$  applied to  $\hat{w}$  does not halt. This is clearly nonsense. The contradiction tells us that our assumption of the existence of H, and hence the assumption of the decidability of the halting problem, must be false.